Short Biography

2023-present Research and innovation manager at the Innovation Defense Agency.

2019-2023 HPC and embedded computing expert for AI at DGA MI.

2009-2019 Research Engineer at CEA, Saclay.

Researcher in

High-Performance and Embedded Computing.

2017-today Research activities in heterogeneous computing.

2015-2017 In charge of CEA LIST partnership in M2DC and Exanode H2020 European projects on micro-servers and parallel chips.

2013-today Organization of the ICCS/Alchemy track on heterogeneous platforms and many-core processors.

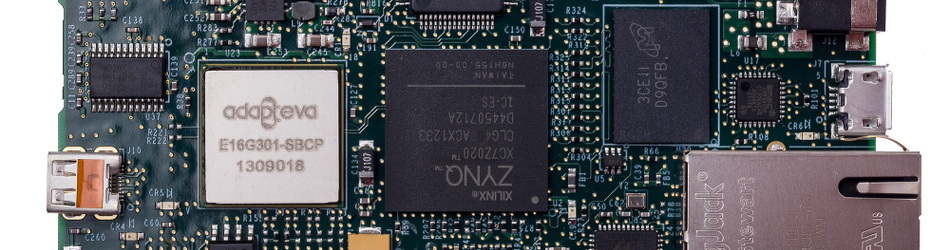

2009-2012 CEA-Kalray joint laboratory: Design and implementation of several steps of the Sigma-C dataflow compilation toolchain for many-core processors.

2017-today Research activities in heterogeneous computing.

2015-2017 In charge of CEA LIST partnership in M2DC and Exanode H2020 European projects on micro-servers and parallel chips.

2013-today Organization of the ICCS/Alchemy track on heterogeneous platforms and many-core processors.

2009-2012 CEA-Kalray joint laboratory: Design and implementation of several steps of the Sigma-C dataflow compilation toolchain for many-core processors.

2005-2008 Ph.D. Candidate at University of Rennes 1, INRIA, Rennes.

Research in Grid

Computing and High Performance Computing under the supervision

of Luc

Bougé

and Gabriel

Antoniu in the PARIS/KerData team.

5-month visit at Sun Microsystems, Santa Clara, USA : Performance evaluation of the JXTA peer-to-peer protocol.

Eligibility Qualifications for Assistant Professor in Computer Science (CNU Section 27) 2010 & 2015.

5-month visit at Sun Microsystems, Santa Clara, USA : Performance evaluation of the JXTA peer-to-peer protocol.

Eligibility Qualifications for Assistant Professor in Computer Science (CNU Section 27) 2010 & 2015.

2003-2005 Master Engineering & Master Research in Computer Science at INSA Rennes.

Internship at INRIA:

Research on data consistency models and protocols for grid

architectures.

Internship at Siradel: Design and implementation of a data exchange format for the Volcano radio propagation model software.

Internship at Siradel: Design and implementation of a data exchange format for the Volcano radio propagation model software.